2025年7月5日49

中国のロボット掃除機大手「北京石頭世紀科技(Roborock )」は6月27日、香港証券取引所のメインボードへの新規株式公開(IPO)を申請した。主幹事はJPモルガン・チェースと中信証券(CITIC Securities)が務める。...

2025年7月5日47

カナダの物流スタートアップ「UniUni」がこのほど、シリーズD1で7000万ドル(約100億円)余りを調達した。米Bessemer Venture Partnersと中国の創新工場(Sinovation Ventures)が共同で出...

2025年7月5日59

中国通信機械大手の華為技術(ファーウェイ)が主導する電気自動車(EV)ブランド連合「鴻蒙智行(HIMA)」は、6月の販売(納車)台数が5万2747台となり、新興勢トップに輝いた。 最も貢献したのは賽力斯集団(SERES)...

2025年7月4日61

トヨタ自動車の中国での販売を手掛ける一汽トヨタ自動車販売は6月28日、北京市から天津市天津経済技術開発区への本社移転を完了したと発表した。設立から22年で初の他省への移転となり、一汽トヨタの天津市での本部機能は一層強化される。...

2025年7月4日48

ディスプレー用ドライバチップ大手の「雲英谷科技(Viewtrix Technology)」が6月26日、香港証券取引所に上場申請書を提出した。 これまでの出資者には、米クアルコムの中国法人、小米集団(シャオミ)傘下の湖北...

2025年7月4日48

中国(香港)と米国を拠点とする人工知能(AI)創薬スタートアップ「Insilico Medicine(インシリコ・メディシン)」がこのほど、シリーズEで約1億2300万ドル(約180億円)を調達したと発表した。資金調達後の評価額は13...

2025年7月4日79

自転車用内装変速機(ギアハブ)の開発・製造を行う中国・洛梵狄智能科技(Lofandi Intelligent Technology)(以下、Lofandi)が、今年5月に開催された中国国際自転車展覧会(CHINA CYCLE 2025...

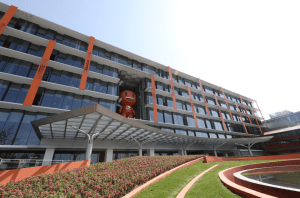

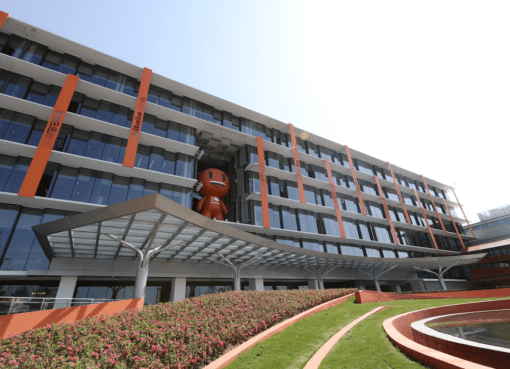

2025年7月4日110

中国電子商取引(EC)大手アリババグループがこのほど発表した2025年3月期通期決算は、売上高が前年比6%増の9963億4700万元(約20兆35億円)、純利益が77%増の1259億7600万元(約2兆5200億円)だった。...

2025年7月3日87

欧州航空機大手エアバスの中国現地法人、エアバス中国の徐崗最高経営責任者(CEO)は、フランス・パリで16日から22日に開かれた第55回パリ航空ショーで新華社のインタビューに応じ、エアバスは中国進出から40年にわたり、中国のパートナーと...

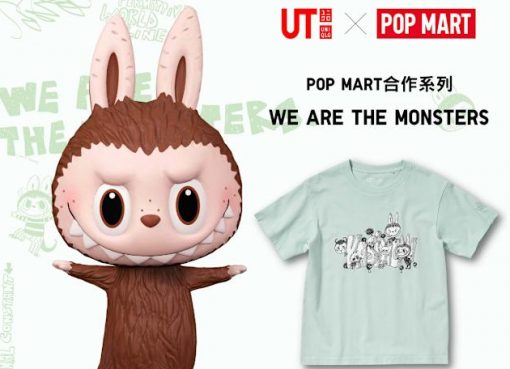

2025年7月3日300

ファーストリテイリング傘下のユニクロはこのほど、中国のアートトイブランド「POP MART(ポップマート)」の人気シリーズ「THE MONSTERS(ザ・モンスターズ)」とのコラボレーションアイテムを8月29日に発売すると発表した。同...

フォローする

フォローする フォローする

フォローする